- Главная

- Блог

- Информационная безопасность

- Декодер и оперативная память — Проектируем свой компьютер, часть 4

Декодер и оперативная память — Проектируем свой компьютер, часть 4

Оглавление

- Начало

- Элементарная ячейка памяти

- Регистр

- Декодер и оперативная память

- Арифметико-логическое устройство

4. Декодер и оперативная память

Описание декодера

Регистр, способный хранить один байт данных это уже неплохо, но как можно работать с более большими объемами информации? Для этого нам необходимо объединить несколько регистров в единую систему.

Но помимо самих регистров в такой системе также должен присутствовать такой элемент как декодер. Сначала посмотрим на него в общих чертах.

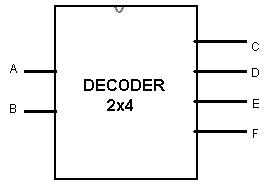

Как видно, у него два входа и четыре выхода. Сходу кажется нелогичным. Давайте сначала вспомним, сколько комбинаций могут образовывать два бита? Четыре: 00, 01, 10, 11. То есть декодер на входе может иметь четыре возможные пары значений. Теперь посмотрим какой выход соответствует каждой из пар.

|

A |

B |

C |

D |

E |

F |

|

0 |

0 |

1 |

0 |

0 |

0 |

|

0 |

1 |

0 |

1 |

0 |

0 |

|

1 |

0 |

0 |

0 |

1 |

0 |

|

1 |

1 |

0 |

0 |

0 |

0 |

Как видно соблюдается следующий паттерн: на одном из выходов декодера всегда единица, а на остальных – ноль. На каком именно выходе будет единица, зависит от входа. То есть декодер так устроен, что каждой уникальной входной комбинации соответствует уникальная выходная комбинация. Поэтому, если декодер имеет два входа, он будет обязательно иметь четыре выхода.

Но декодер может принимать и больше входных значений. Например, три. Но три бита могут образовывать уже 8 комбинаций, поэтому в таком случае декодер должен иметь и восемь выходов. Если четыре входа, то 16 выходов и т.д.

Построение декодера

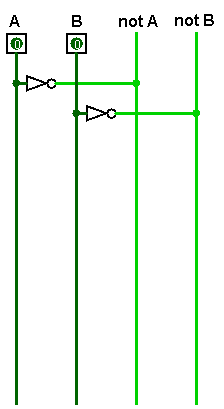

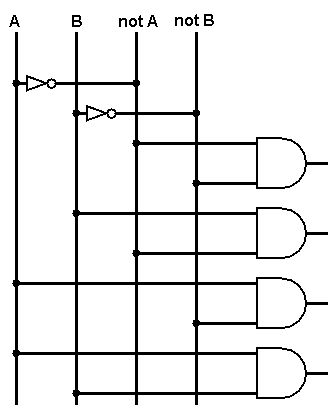

Теперь, построим такую штуку из логических элементов. Сначала для простоты начнем с декодера 2x4.

Итак, мы видим четыре провода. Значения, которые имеют первые два (A и B) задаются нами, значения notA и notB представляют собой отрицания значений A и B. Всего эти четыре провода могут нести четыре уникальных комбинаций.

|

A |

B |

not A |

not B |

|

0 |

0 |

1 |

1 |

|

0 |

1 |

1 |

0 |

|

1 |

0 |

0 |

1 |

|

1 |

1 |

0 |

0 |

Можно заметить, что в любой из возможных комбинаций два каких-либо провода всегда несут единицы, а два других всегда ноль. Используем это свойство для построения декодера. Применим логический гейт AND, который выдает единицу только когда на всех его входах подаются единицы.

Итак, когда два каких-либо провода несут единицы они также передают эти единицы определенному AND-гейту и следовательно этот гейт на выходе будет иметь единицу. Другие же AND-гейты выдают в это время ноль, поскольку либо на одном либо на обоих проводах, с которых они берут входящие значения, будет присутствовать ноль.

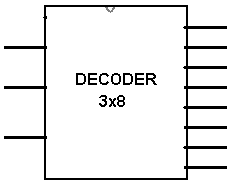

Основываясь на этом же принципе можно построить декодер 3x8, но для этого нам также потребуется AND-гейт с тремя входами.

Смысл его работы такой же: он выдает единицу только, когда на всех (трех) его входах единицы, а в остальных случаях он выдает ноль.

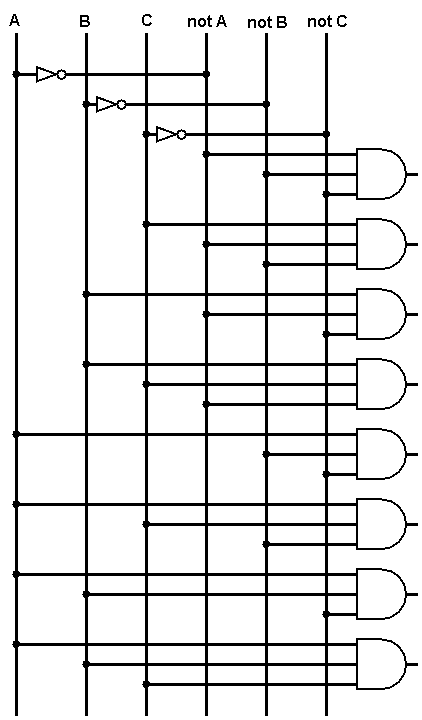

Теперь посмотрим на декодер 3x8

Его отличие от предыдущего в том, что в нем три провода всегда будут нести единицу, а три других всегда ноль. Поэтому мы используем AND-гейт с тремя входами.

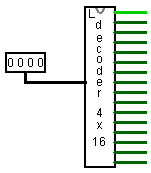

По такому же принципу работает декодер 4x16, который мы будем использовать в схеме оперативной памяти.

Структура оперативной памяти

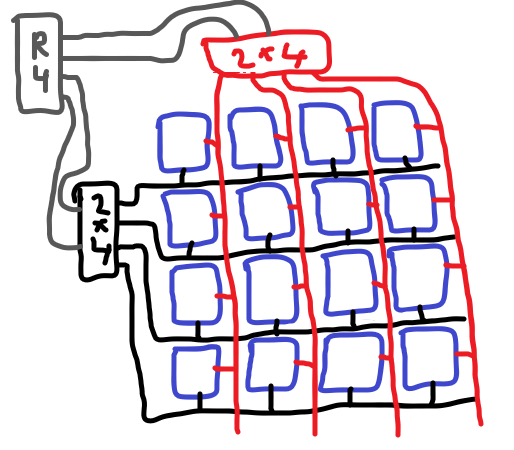

Представим, что у нас есть 16 ячеек памяти по одному байту. Как нам с ними работать? Сначала сгруппируем их в виде таблицы 4x4. Потом добавим к каждой из низ два входа (горизонтальный и вертикальный). Потом берем два декодера 2x4 и подключаем их таким образом. Сами декодеры получает свои значения из блока памяти размером 4 бита.

Что бы получить доступ к определенной ячейке, надо подать на оба ее входа единицы. Как видно это делается с помощью блока R4. Его бы будем называть адресный регистр. Он представляет собой блок памяти размером в 4 бита. Мы помещаем в этот блок набор из четырех битов, эти биты передаются на декодеры. В зависимости от входного значения горизонтальный декодер передает единицу на горизонтальные входы всех ячеек определенного столбца. Вертикальный декодер передает единицу на вертикальные входы всех ячеек определенной строки. Ячейка памяти, которая находится на пересечении получает единицы на оба своих входа. Так мы можем выбирать ячейку, с которой хотим работать. Комбинация битов, которую нужно поместить в блок R4, что бы выбрать определенную ячейку называется адресом ячейки. Конечно, нужно также спроектировать саму ячейку таким образом, что бы она “знала” что если на определенных ее входах единицы, то она может принимать либо отправлять данные. Сейчас этим займемся.

Ячейка памяти

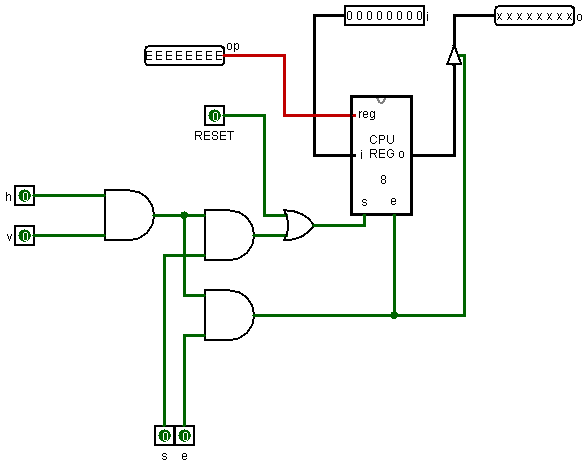

Сразу перейдем к схеме.

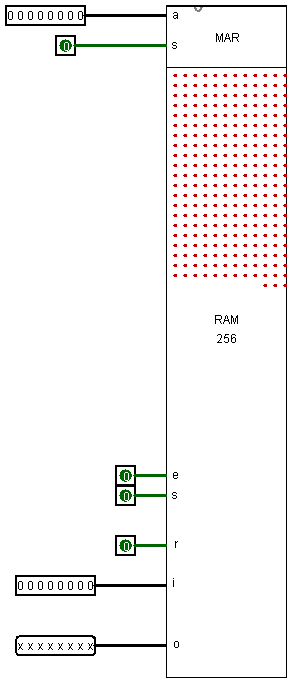

Как мы видим, центральным элементом ячейки является регистр, устройство которого мы уже описывали ранее. Входы v (vertical – вертикальный) и h (horizontal – горизонтальный) это те самые входы, значение на которые подаются декодерами. Если на обоих этих входах единицы, то мы можем открывать и закрывать регистр для записи, а также считывать с него информацию , используя для этого входы s и e (к каждой ячейке также подключен вход i для записи данных на регистр и выход o для вывода этих данных). Реализацию оперативной памяти размером в 256 байт можете посмотреть сами, скачав симулятор logisim и загрузив в него схему. Все ссылки будут в источниках. Мы посмотрим на модуль памяти целиком.

Верхние входы ведут к адресному регистру, размером в один байт. На вход a мы подаем адрес ячейки, вход s делает доступным либо нет адресный регистр для приема информации. Остальные входы предназначены для работы с выбранной нами ячейкой памяти и были разобраны выше. Вход r, если активен позволяет модифицировать все ячейки памяти целиком: мы передаем некоторое значение на вход a и это значение записывается уже на все ячейки.

Источники

- John Clark Scott “But How Do It Know?”

- Logisim – программа для симуляции логических схем (www.cburch.com/logisim/)

- ScottCPU – название модели компьютера, который мы проектируем, скачать его схему для logisim’а можно тут: www.buthowdoitknow.com/downloads/CPU_DESIGN.circ